#### (19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B1)

FL

(11)特許番号

特許第6545889号 (P6545889)

最終頁に続く

(45) 発行日 令和1年7月17日(2019.7.17)

(24) 登録日 令和1年6月28日 (2019.6.28)

器興区 ウォンゴメ路 12

| HO1L 33/48   | <b>(2010.01)</b> HO1L        | 33/48     |                          |

|--------------|------------------------------|-----------|--------------------------|

| HO1L 21/673  | <b>(2006.01)</b> HO1L        | 21/68     | U                        |

| HO1L 21/677  | <b>(2006.01)</b> HO1L        | 21/68     | В                        |

| HO1L 21/60   | <b>(2006.01)</b> HO1L        | 21/60     | 3 1 1 T                  |

| HO5K 13/04   | <b>(2006.01)</b> HO5K        | 13/04     | В                        |

|              |                              |           | 請求項の数 10 (全 17 頁) 最終頁に続く |

| (21) 出願番号    | 特願2018-230832 (P2018-230832) | (73) 特許権者 | 者 514121240              |

| (22) 出願日     | 平成30年12月10日 (2018.12.10)     |           | ルーメンス カンパニー リミテッド        |

| 審査請求日        | 平成30年12月10日 (2018.12.10)     |           | 大韓民国 449-901 キョンギ道       |

| (31) 優先権主張番号 | 10-2018-0018125              |           | ヨンイン市 キヘン区 ウォンゴメ - ロ     |

| (32) 優先日     | 平成30年2月14日 (2018.2.14)       |           | 1 2                      |

| (33) 優先権主張国  | 韓国(KR)                       | (74) 代理人  | 110000051                |

| (31) 優先権主張番号 | 10-2018-0123402              |           | 特許業務法人共生国際特許事務所          |

| (32) 優先日     | 平成30年10月16日 (2018.10.16)     | (72) 発明者  | ユ,テキョン                   |

| (33) 優先権主張国  | 韓国 (KR)                      |           | 大韓民国 17086 京畿道 龍仁市       |

|              |                              |           | 器興区 ウォンゴメ路 12            |

| 早期審査対象出願     |                              | (72) 発明者  | ソ,ジュオック                  |

|              |                              |           | 大韓民国 17086 京畿道 龍仁市       |

|              |                              | 11        |                          |

(54) 【発明の名称】 LEDディスプレイパネル製造のためのマイクロLEDチップアレイ方法及びこれに用いられる マルチチップキャリア

#### (57)【特許請求の範囲】

# 【請求項1】

サクションホールを通じて減圧される複数のチップポケットが形成されたマルチチップ キャリアを準備する段階と、

各マイクロLEDチップのそれぞれ<u>の発光面が前記各チップポケットの底と接し、前記各マイクロLEDチップのそれぞれの電極パッドが前記各チップポケットの外側に出るように、</u>前記各マイクロLEDチップを前記各チップポケットにキャプチャリングする段階と、

<u>前記各電極パッドが接着フィルムに接するように</u>前記各チップポケットにキャプチャリングされた前記各マイクロLEDチップを<u>前記接着フィルム</u>上にプレーシングする段階と

前記各マイクロLEDチップの発光面がトランスファーフィルムに接するように前記接 着フィルムにプレーシングされた前記各マイクロLEDチップを前記トランスファーフィ ルム上に付着する段階と、

<u>前記トランスファーフィルムに付着した前記各マイクロLEDチップをマウント基板上</u>に転写する段階と、を含み、

前記各チップポケットのそれぞれは、前記底より大きい幅を有する入口から前記底まで つながったスロープを含み、

前記スロープにより、前記<u>接着フィルム</u>上にプレーシングされた前記各マイクロLEDチップの中心間の間隔と前記各チップポケットの中心間の間隔とが同一であり、

前記各マイクロLEDチップを前記トランスファーフィルム上に付着する段階は、前記 発光面が前記トランスファーフィルムと接した状態で加圧ローラーを用いて前記トランス ファーフィルムを加圧する段階を含み、

前記各マイクロLEDチップを前記マウント基板上に転写する段階は、前記各電極パッドが前記マウント基板上の各電極と近接した状態で加圧ローラーを用いて前記トランスファーフィルムを加圧する段階を含むことを特徴とするマイクロLEDチップアレイ方法。

#### 【請求項2】

前記スロープにより、前記各チップポケット内に整列された前記各マイクロLEDチップのそれぞれの動きを規制することを特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

10

# 【請求項3】

前記各チップポケットのそれぞれの深さは、前記各マイクロLEDチップのそれぞれの厚さより小さいことを特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

# 【請求項4】

前記サクションホールは、前記マルチチップキャリアの前記底で前記各チップポケットのそれぞれに連結されて形成されることを特徴とする請求項 1 に記載のマイクロLEDチップアレイ方法。

#### 【請求項5】

前記各チップポケットのそれぞれに対する各サクションホールの個数は、複数個であることを特徴とする請求項4に記載のマイクロLEDチップアレイ方法。

20

#### 【請求項6】

前記マルチチップキャリアは、サクションプレートの一面に前記各チップポケットを形成し、前記サクションプレートの他面に前記各チップポケットの底で前記各チップポケットと連結される各サクションホールを形成したことを特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

#### 【請求項7】

前記プレーシングする段階では、前記各マイクロLEDチップが前記<u>接着フィルム</u>上に置かれた状態で前記各チップポケット内部の圧力を増加させることを特徴とする請求項 1 に記載のマイクロLEDチップアレイ方法。

# 【請求項8】

30

前記キャプチャリングする段階において、前記マイクロLEDチップの電極パッドは、前記マルチチップキャリアで前記各チップポケットを基準にして上側に位置し、前記プレーシングする段階において、前記マイクロLEDチップの電極パッドは、前記マルチチップキャリアで前記各チップポケットを基準にして下側に位置することを特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

# 【請求項9】

前記キャプチャリングする段階後、前記各チップポケットのそれぞれに前記マイクロLEDチップが整列された前記マルチチップキャリアを180度回転させることを特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

# 【請求項10】

40

<u>前記チップポケットの底の横幅は、前記マイクロLEDチップの横幅と同じであること</u>を特徴とする請求項1に記載のマイクロLEDチップアレイ方法。

# 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、LEDディスプレイパネル製造技術に係り、より詳しくは、マイクロLED製造のためのマイクロLEDチップアレイ方法及びこれに用いられるマルチチップキャリアに関する。

#### 【背景技術】

[0002]

マイクロLEDディスプレイパネルを具現するためのマイクロLEDモジュールを製造するために、垂直型又はフリップチップ型の各マイクロLEDチップをPCB(Printed Сircuit Board)などの基板にボンディングしてアレイする。このためには、チップ維持フィルム上にソーティング(sorting)されている各マイクロLEDチップを基板上の各ソルダーの位置に正確に移してボンディングすることが要求される。

#### [0003]

このとき、チップ維持フィルム上にソーティングされている各マイクロLEDチップの間隔は基板上の各ソルダーの間隔と異なるので、基板上の各ソルダーの位置を一つずつ確認した後、ダイボンダーを用いてマイクロLEDチップを基板上の該当のソルダーにボンディングする方法が提案されたことがある。しかし、この方法は、多数のマイクロLEDチップを一つずつ移して基板上にボンディングしなければならないので、過度に多くの工程時間が要求されるという短所を有する。

### [0004]

代案的に、ソーティングされたチップ維持フィルム上のマイクロLEDチップをピクセルサイズに合わせて再配列した後、全体のマイクロLEDチップを、例えば、ロールツーロール(roll to roll)方式又は静電気接着方式などで転写する方法がある。このような方法を用いる場合、マイクロLEDディスプレイパネルを量産するためには、再配列時に各マイクロLEDチップにおけるチップ間の間隔の精密度が数  $\mu$  m以内でなければならず、速度も速くなければならないが、これを満足させることが難しかった。更に、マイクロLEDチップより大きいサイズを有する各LEDチップを用いるミニLEDディスプレイパネルの量産においても、各LEDチップにおけるチップ間の間隔の精密度が±10 $\mu$ m以内を満足させなければならないが、これも達成することが難しかった。

#### [0005]

また、ロールツーロール方式又は静電気接着方式などで一般的に各LEDチップを転写する場合、再配列した各LEDチップの上部(すなわち、LED発光面)に接着シートを付着させた状態で転写を進行しなければならず、後で接着シートを除去するとき、LEDチップの上部に接着剤が少しでも残っていると発光効率が低下するという問題がある。

#### [0006]

また、基板に各LEDチップを転写するために検討されてきた様々な方法は、ディスプレイを具現するのに十分な各LEDチップのX/Y/Z正配列水準に合致しておらず、各LEDチップをボンディングするためのリフロー工程においても、各LEDチップの所望でない回転や捩れなどの現象が発生する憂いが大きかった。

### 【先行技術文献】

#### 【特許文献】

#### [0007]

【特許文献1】特開2018-60993

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0008]

本発明の目的は、各マイクロLEDチップのような微細なサイズの各LEDチップを任意の位置で基板に移してアレイするにおいて、各LEDチップの精密でない配列問題を解決し、多量のLEDチップを一度に基材上にアレイする方法を提供することにある。

本発明の他の目的は、各マイクロLEDチップのような微細なサイズの各LEDチップをばらつきなしで容易に集めて基材上に正確に移すのに用いられるマルチチップキャリアを提供することにある。

#### 【課題を解決するための手段】

### [0009]

本発明の一側面に係るマイクロLEDチップアレイ方法は、サクションホールを通じて減圧される複数のチップポケットが形成されたマルチチップキャリアを準備する段階と、

10

20

30

30

40

前記各マイクロLEDチップのそれぞれが前記各チップポケットのそれぞれの底に密着し、前記各マイクロLEDチップを前記各チップポケットにキャプチャリングする段階と、前記各チップポケットにキャプチャリングされた前記各マイクロLEDチップを基材上にプレーシングする段階とを含み、前記各チップポケットのそれぞれは、前記底より大きい幅を有する入口から前記底までつながったスロープを含み、前記スロープにより、前記基材上にプレーシングされた各マイクロLEDチップの中心間の間隔と前記各チップポケットの中心間の間隔とが同一である。

#### [0010]

一実施例において、前記スロープにより、前記各チップポケット内に整列された前記各マイクロLEDチップのそれぞれの動きを規制する。

10

# [0011]

一実施例において、前記各チップポケットのそれぞれの深さは、前記各マイクロLEDチップのそれぞれの厚さより小さい。

# [0012]

一実施例において、前記サクションホールは、前記マルチチップキャリアの前記底で前記各チップポケットのそれぞれに連結されて形成される。

#### [0013]

一実施例において、前記各チップポケットのそれぞれに対する各サクションホールの個数は複数個である。

20

### [0014]

一実施例において、前記マルチチップキャリアは、サクションプレートの一面に前記各チップポケットを形成し、前記サクションプレートの他面に前記各チップポケットの底で前記各チップポケットと連結される各サクションホールを形成する。

#### [0015]

一実施例において、前記プレーシングする段階は、前記各マイクロLEDチップが前記基材上に置かれた状態で前記各チップポケット内部の圧力を増加させることを含む。

#### [0016]

一実施例において、前記キャプチャリングする段階において、前記マイクロLEDチップの電極パッドは、前記マルチチップキャリアで前記各チップポケットを基準にして上側に位置し、前記プレーシングする段階において、前記マイクロLEDチップの電極パッドは、前記マルチチップキャリアで前記各チップポケットを基準にして下側に位置する。

30

# [0017]

一実施例において、前記方法は、前記キャプチャリングする段階後に、前記各チップポケットのそれぞれに前記マイクロLEDチップが整列された前記マルチチップキャリアを180度回転させることを含む。

#### [0018]

一実施例において、前記キャプチャリングする段階は、前記各マイクロLEDチップのそれぞれの発光面が前記底と接し、前記各マイクロLEDチップのそれぞれの電極パッドが前記各チップポケットの外側に出るように、前記各マイクロLEDチップを前記各チップポケットにキャプチャリングする。

40

# [0019]

一実施例において、前記基材は、電極を有するマウント基板であって、前記プレーシングする段階では、前記電極パッドが前記電極に近接するように前記各マイクロ L E D チップを前記マウント基板上にプレーシングする。

#### [0020]

一実施例において、前記基材は接着フィルムであって、前記プレーシングする段階では、前記電極パッドが前記接着フィルムに付着するように前記各マイクロ L E D チップを前記接着フィルム上にプレーシングすることを含む。

#### [0021]

一実施例において、前記方法は、前記接着フィルム上に付着した各マイクロLEDチッ

プをマウント基板上に転写する段階を更に含む。

#### [0022]

一実施例において、前記キャプチャリングする段階では、前記各マイクロLEDチップ のそれぞれの電極パッド側が前記底と接し、前記各マイクロLEDチップのそれぞれの発 光面が前記各チップポケットの外側に出るように、前記各マイクロLEDチップを前記各 チップポケットにキャプチャリングすることを含む。

#### [0023]

本発明の一側面において、複数のマイクロLEDチップを一定の配列で整列し、その整 列された各マイクロLEDチップを基材上にプレーシングするためのマルチチップキャリ アが提供され、前記マルチチップキャリアは、前記複数のマイクロLEDチップを吸入す るように、サクションプレートの一面に一定の配列で形成された複数のチップポケットを 含み、前記各チップポケットのそれぞれの底の形状及びサイズは、該当のチップポケット に吸入された各マイクロLEDチップのそれぞれの動きを規制するように定められ、前記 各チップポケットのそれぞれは、前記底より大きい幅を有する入口から前記底までつなが ったスロープを含む。

#### [0024]

一実施例において、前記各チップポケットのそれぞれの深さは、前記各マイクロLED チップのそれぞれの厚さより小さい。

#### [0025]

一実施例において、前記マルチチップキャリアは、前記各チップポケットのそれぞれの 底で前記各チップポケットのそれぞれに連結される複数のサクションホールを更に含む。

#### [0026]

一実施例において、前記各チップポケットのそれぞれに対する各サクションホールの個 数は複数個である。

#### [0027]

一実施例において、前記各サクションホールは外部真空源と連結される。

- 実施例において、前記マルチチップキャリアは、Si、GaAs、サファイア又はA 1N材料で形成される。

### 【発明の効果】

[0029]

本発明の各効果は、以下の実施例の説明からより良く理解されるだろう。

【図面の簡単な説明】

#### [0030]

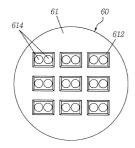

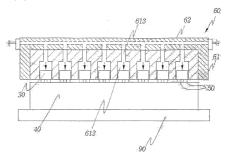

【図1】本発明の一実施例に係るマルチチップキャリアを説明するための平面図である。

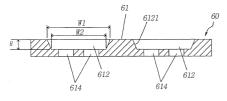

【図2】本発明の一実施例に係るマルチチップキャリアの一部を拡大して示した断面図で ある。

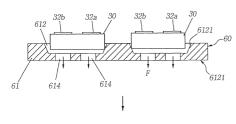

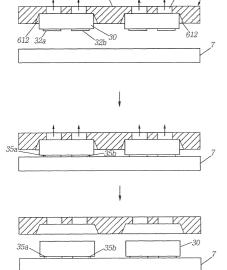

【図3】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法の 一実施例を説明するための図である。

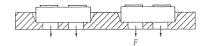

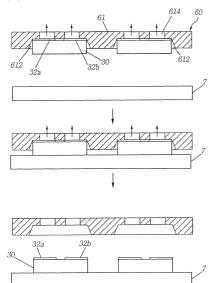

40 【図4】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法の - 実施例を説明するための図である。

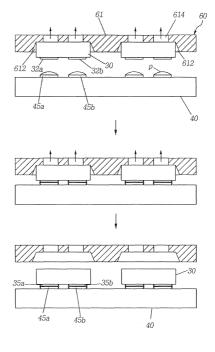

【図5】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法の 他の実施例を説明するための図である。

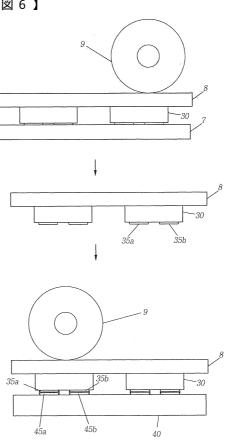

【図6】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法の 他の実施例を説明するための図である。

【図7】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法を 説明するための図である。

【図8】図1及び図2に示したマルチチップキャリアを用いたLEDチップアレイ方法を 説明するための図である。

【図9】本発明の更に他の実施例に係るLEDチップアレイ方法を全般的に説明するため

10

20

30

のフローチャートである。

【図10】図9に示したチップアレイ方法において、各マイクロLEDチップが維持されているチップ維持フィルム及びソルダーが形成されている基板を説明するための図である

【図11】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図12】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図13】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図14】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図15】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図16】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図17】図9に示したLEDチップアレイ方法の各段階を説明するための図である。

【図18】図18は、基板及びその基板上にアレイされた各マイクロLEDチップが発熱 ブロックから分離された状態を示す。

【発明を実施するための形態】

#### [0031]

以下、本発明の好適な各実施例を各図面を参照して詳細に説明する。

#### [0032]

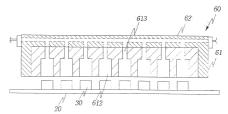

図 1 乃至図 4 を参照して、本発明の一実施例に係るマルチチップキャリアを用いた L E D チップアレイ方法を説明する。

#### [0033]

本発明の一実施例に係るLEDチップアレイ方法は、マルチチップキャリア準備段階と、チップキャプチャリング段階と、チッププレーシング段階と、を含む。

#### [0034]

マルチチップキャリア準備段階では、複数のマイクロLEDチップをキャプチャリングし、そのキャプチャリングされた複数のマイクロLEDチップをマウント基板にプレーシングするマルチチップキャリア60が図1及び図2に示したように準備される。マルチチップキャリア60の外部形状は、図示したように、略円形であってもよく、四角形又はそれ他の形状であってもよい。

#### [0035]

マルチチップキャリア60は、一面に複数のチップポケット612が一定の配列で形成されたサクションプレート61を含む。また、サクションプレート61は、各チップポケット612のそれぞれに対応するように形成された各サクションホール614を含む。各サクションホール614は、各チップポケット612が形成されたサクションプレート61の一面の反対面に形成された状態で、各チップポケット612のそれぞれの底面で各チップポケット612と連結されている。各サクションホール614のそれぞれは、対応するチップポケット612の内部圧力を減圧し、マイクロLEDチップ30をチップポケット612内に吸入するためのものであって、外部真空源と連結される。チップポケット612内に吸入された状態で収容されているマイクロLEDチップは、チップポケット612内の圧力を増加させると、チップポケット612から分離される状態となる。一つのチップポケット612に対するサクションホール614の個数は複数個であることが好ましい。

#### [0036]

マルチチップキャリア60のサクションプレート61は、Si、GaAs、サファイア 又はA1Nなどの材料からなる。また、各チップポケット612は、一定の深さHを有し 、チップポケット612の深さは、サクションされるマイクロLEDチップの厚さより小 さく定められる。ここで、マイクロLEDチップの厚さは、マイクロLEDチップの光放 出面から電極パッドの表面までの距離を意味する。また、チップポケット612は、入口 の横幅W1が底の横幅W2より大きく形成されており、横幅W1を有する入口から横幅W 2を有する底までつながったスロープ6121を有する。チップポケット612の入口の 横幅W1は、マイクロLEDチップの横幅より大きく、チップポケット612の底の横幅 10

20

30

40

20

30

40

50

W2は、マイクロLEDチップの横幅と同じである。ここで、「同じである」という意味は、無視できる程度の誤差範囲内であるということである。図面には示していないが、チップポケットの入口の縦幅は、チップポケットの底の縦幅より大きく、マイクロLEDチップの縦幅は、チップポケットの入口の縦幅より大きく、チップポケットの底の縦幅とほぼ同じである。

### [0037]

図3を参照すると、前記チップキャプチャリング段階は、サクションホール614と接 続された外部真空源の作動によってサクションホール614の内部が減圧され、その結果 、チップポケット612の入口に少なくとも一部が載せられていたマイクロLEDチップ 30がチップポケット612内に落下しながらチップポケット612の底に載置される。 そして、サクションホール614を通じた真空吸入力Fにより、マイクロLEDチップ3 0 がチップポケット 6 1 2 の底に吸着して分離されない状態となる。上述したように、チ ップポケット612の入口から底までつながったスロープ6121により、マイクロLE Dチップ30は、チップポケット612内に円滑に挿入できると同時に、チップポケット 6 1 2 の底に載置されたときにチップポケット 6 1 2 の底の幅とマイクロLEDチップの 幅とがほぼ一致することによって、チップポケット612内で移動することなく正確な位 置に固定される。よって、各チップポケット612に一つずつ入って維持された各マイク ロLEDチップ30は、各チップポケット612の中心間の間隔と同じ中心間の間隔で配 列され、チップポケット612内の真空減圧状態が解除されない以上、各チップポケット 6 1 2 に収容されている各マイクロ L E D チップ 3 0 の配列とそれらの間の間隔は変化す ることなく一定である。例えば、各チップポケットに吸入されている各マイクロLEDチ ップ30を任意の位置に下ろすときの力によって微細な誤差が発生し得る。この理由又は その他の理由により、配列後の各マイクロLEDチップ30の中心間の間隔と各チップポ ケット612の中心間の間隔とが完全に同じであることは実質的に不可能である。よって 、配列後の各マイクロLEDチップ30の中心間の間隔と各チップポケット612の中心 間の間隔とが完全に同じでないとしても、実質的に同じであれば十分である。したがって 、本明細書において、各マイクロLEDチップ30の中心間の間隔と各チップポケット6 12の中心間の間隔とが同じであることは、これらが5μm以内の偏差範囲内で同じであ ることを意味する。

# [0038]

各マイクロLEDチップ30がプレーシングされる基材(base body or base plate)が、各電極45a、45b(図4参照)を備えたマウント基板4 0(図4参照)上であるので、マイクロLEDチップ30は、チップポケット612の底面に吸着する面の反対側面に各電極45a、45b(図4参照)に対応する電極パッド3 2a、32bを備える。すなわち、マルチチップキャリア60は、自身のチップポケット612内にマイクロLEDチップ30を吸入し、マイクロLEDチップ30の発光面がチップポケット612の底面と接するように、そして、電極パッド32a、32bがチップポケット612の外側に出るようにマイクロLEDチップ30を収容・維持する。本実施例では、チップキャプチャリング段階において、チップポケット612が上側に向かっているが、真空吸入力と共に重力がマイクロLEDチップ30に作用し、マイクロLEDチップ30がより円滑にチップポケット612に入り込むようになる。

# [0039]

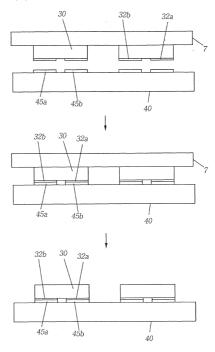

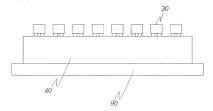

図4を参照すると、マルチチップキャリア60が180度回転してひっくり返され、各チップポケット612及びその各チップポケット612に吸入された各マイクロLEDチップ30がその下側に位置したマウント基板40に向かうようになり、次に、各マイクロLEDチップ30がマウント基板40にプレーシングされるまでマルチチップキャリア60が下降するか、又はマウント基板40が上昇する。上述したように、チップポケット612の深さがマイクロLEDチップ30の厚さより小さいので、マルチチップキャリア60が最大に下降するか、又はマウント基板40が最大に上昇するとき、マイクロLEDチップ30に備えられた各電極パッド32a、32bがマウント基板40の各電極45a、

45 bと接するか又は近接するようになる。電極 45 a、 45 b上には、ボンディング物質 p が予め塗布されていてもよい。マイクロLEDチップ 30 がマウント基板 40 上にプレーシングされた状態で、例えば、サクションホール 61 4 と連結された外部真空源の作動を停止するか、又は他の方式でチップポケット 61 2 内の圧力が減少し、その結果、各マイクロLEDチップ 30 が各チップポケット 61 2 から分離される。

#### [0040]

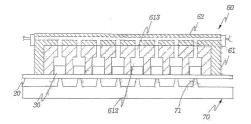

図 5 及び図 6 を参照して、図 1 及び図 2 に示したマルチチップキャリア 6 0 を用いた LEDチップアレイ方法の他の実施例を説明する。

#### [0041]

本実施例に係るLEDチップアレイ方法も、上述した実施例と同様に、マルチチップキャリア準備段階と、チップキャプチャリング段階と、チッププレーシング段階とを含む。 これに加えて、前記LEDチップアレイ方法はチップ転写段階を更に含む。

#### [0042]

マルチチップキャリア準備段階では、上述した実施例と実質的に同一の方式でマルチチップキャリア60が準備される。

#### [0043]

上述した実施例において、各マイクロLEDチップ30がマルチチップキャリア60によってピックアップされてプレーシングされる部分が、各電極を含むマウント基板であったが、本実施例では、マウント基板でない接着フィルム7の表面上である。

### [0044]

図5を参照すると、各マイクロLEDチップ30がマルチチップキャリア60のチップポケット612に吸入されることで、各マイクロLEDチップ30は既に設定された間隔で整列される。これは、チップポケット612の底が、その底に密着したマイクロLEDチップ30の前後左右の動きを規制できる形状、すなわち、マイクロLEDチップ30の形状に対応する形状を有することによって可能である。このとき、マイクロLEDチップ30は、チップポケット612の底面に吸着する面の反対側面に各電極45a、45bに対応する電極パッド32a、32bを備える。すなわち、マルチチップキャリア60は、自身のチップポケット612内にマイクロLEDチップ30を吸入し、マイクロLEDチップ30の発光面がチップポケット612の底面と接するように、そして、電極パッド32a、32bがチップポケット612の外側に出るようにマイクロLEDチップ30を収容・維持する。

# [0045]

上述した実施例と同様に、チップポケット612の入口から底までつながったスロープ6121により、マイクロLEDチップ30はチップポケット612内に円滑に挿入される。上述した実施例で説明したように、各チップポケット612に一つずつ入って維持された各マイクロLEDチップ30は、各チップポケット612の中心間の間隔と同じ中心間の間隔で配列され、チップポケット612内の真空減圧状態が解除されない以上、各チップポケット612に収容されている各マイクロLEDチップ30の配列とそれらの間の間隔は変化することなく一定である。

#### [0046]

また、マルチチップキャリア60は、上述した実施例において、各マイクロLEDチップ30をマウント基板上にプレーシングするのと類似する方式で、各チップポケット612に吸入されて維持された各マイクロLEDチップ30を接着フィルム7上にプレーシングする。各マイクロLEDチップ30が接着フィルム7上に接着した状態で、より具体的には、各マイクロLEDチップ30の各電極パッド32a、32bが接着フィルム7に接着した状態で、各マイクロLEDチップ30を吸入・維持していたチップポケット612内の圧力が減少し、各マイクロLEDチップ30に対する吸入力が除去され、その結果、各マイクロLEDチップ30はマルチチップキャリア60から分離された状態で接着フィルム7に接着する。

# [0047]

20

10

30

20

30

40

50

本実施例では、接着フィルム7上に所望の間隔及び配列で各マイクロLEDチップ30が整列された後、チップ転写段階が追加的に行われる。図6に示したように、このチップ転写段階では、接着フィルム7上の各マイクロLEDチップ30を、接着性を有するトランスファーフィルム8に元の配列通りに付着させる段階と、トランスファーフィルム8に付着したマイクロLEDチップ30をマウント基板40上にその配列通りに移す段階とを含む。このとき、マイクロLEDチップ30をトランスファーフィルム8及びマウント基板40に対して加圧するために加圧ローラー9が利用可能である。

#### [0048]

各マイクロLEDチップ30の発光面側がトランスファーフィルム8に接着し、その反対側がマウント基板40側に向かうようになる。上述した実施例と同様に、マウント基板40は、各マイクロLEDチップ30の各電極パッド32a、32bに対応する電極45a、45bを上面に備える。トランスファーフィルム8に整列された各マイクロLEDチップ30は、その整列通りにマウント基板40上に転写されるが、このとき、マイクロLEDチップ30の各電極パッド32a、32bは、マウント基板40の各電極45a、45bのそれぞれにボンディングされる。ボンディングには、ソルダー又は導電性ボンディング材料が利用可能である。

#### [0049]

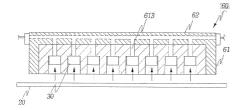

図 7 及び図 8 を参照して、図 1 及び図 2 に示したマルチチップキャリアを用いたLEDチップアレイ方法の更に他の実施例を説明する。

#### [0050]

本実施例に係るLEDチップアレイ方法も、上述した実施例と同様に、マルチチップキャリア準備段階と、チップキャプチャリング段階と、チッププレーシング段階と、を含む。これに加えて、前記チップアレイ方法はチップ転写段階を更に含む。

#### [0051]

マルチチップキャリア準備段階では、上述した実施例と実質的に同じ方式でマルチチップキャリア 6 0 が準備される。

#### [0052]

各マイクロLEDチップ30がマルチチップキャリア60によってピックアップされて プレーシングされる部分は、接着フィルム7の表面上である。

# [0053]

図7を参照すると、各マイクロLEDチップ30がマルチチップキャリア60のチップポケット612に吸入されることで、各マイクロLEDチップ30は既に設定された間隔で整列される。これは、チップポケット612の底が、その底に密着したマイクロLEDチップ30の前後左右の動きを規制できる形状、すなわち、マイクロLEDチップ30の形状に対応する形状を有することによって可能である。上述した各実施例と異なり、マルチチップキャリア60は、自身のチップポケット612内にマイクロLEDチップ30を吸入し、マイクロLEDチップ30の電極パッド32a、32b側がチップポケット612の底と接するように、そして、マイクロLEDチップ30の電極パッドの反対側発光面がチップポケット612の外側に出るようにマイクロLEDチップ30を収容・維持する

# [0054]

マルチチップキャリア60は、各チップポケット612に吸入・維持された各マイクロLEDチップ30を接着フィルム7上にプレーシングする。各マイクロLEDチップ30が接着フィルム7上に接着した状態で、より具体的には、各マイクロLEDチップ30の電極パッドの反対側発光面が接着フィルム7に接着した状態で、各マイクロLEDチップ30を吸入・維持していたチップポケット612内の圧力が減少し、各マイクロLEDチップ30に対する吸入力が除去され、その結果、各マイクロLEDチップ30は、マルチチップキャリア60から分離された状態で接着フィルム7に接着する。

#### [0055]

本実施例では、接着フィルム7上に所望の間隔及び配列で各マイクロLEDチップ30

20

30

40

50

が整列された後、チップ転写段階が追加的に行われる。図 8 に示したように、このチップ 転写段階では、上述した実施例のような別途のトランスファーフィルム 8 を用いることな く、接着フィルム 7 上の各マイクロLEDチップ 3 0 を直接マウント基板 4 0 上にその配 列通りに移す。このとき、マイクロLEDチップ 3 0 の各電極パッド 3 2 a、 3 2 b は、 マウント基板 4 0 の各電極 4 5 a、 4 5 b のそれぞれにボンディングされる。ボンディン グには、ソルダー又は導電性ボンディング材料が利用可能である。

#### [0056]

次に、接着フィルム7が除去される。

#### [0057]

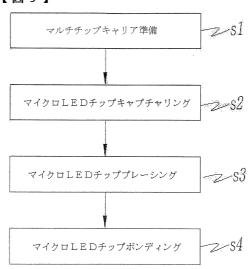

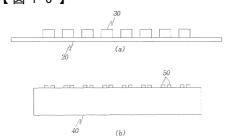

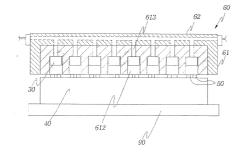

図9は、本発明の更に他の実施例に係るLEDチップアレイ方法を全般的に説明するためのフローチャートで、図10の(a)及び(b)は、図9に示したチップアレイ方法において、各マイクロLEDチップ30が維持されているチップ維持フィルム20及び各ソルダーが形成されている基板40を説明するための図で、図11乃至図18は、図9に示したLEDチップアレイ方法の各段階を説明するための図である。

#### [0058]

図9を参照すると、本発明の一実施例に係るLEDチップアレイ方法は、チップ維持フィルムの上面に維持された各マイクロLEDチップを既に決定された配列で基板上にアレイするLEDチップアレイ方法であって、前記既に決定された配列と一致する配列の各チップポケットが形成されたマルチチップキャリアを準備する段階(s1)と、前記各チップポケットの内部を減圧し、前記各チップポケットのそれぞれに前記各マイクロLEDチップのそれぞれをキャプチャリングする段階(s2)と、前記各チップポケットの配列通りに前記各マイクロLEDチップを前記基板上にプレーシングする段階(s3)と、前記各ソルダーを加熱し、前記各マイクロLEDチップを前記基板上にボンディングする段階(s4)とを含む。

# [0059]

図 1 0 の (a) 及び (b) は、各マイクロLEDチップ 3 0 が維持されているチップ維持フィルム 2 0 と、各ソルダー 5 0 が形成されている基板 4 0 とを示す。

#### [0060]

各マイクロLEDチップ30は、底面に極性が異なる二つの電極を有するフリップチップ型マイクロLEDチップであってもよく、底面に一つの電極を有する垂直型マイクロLEDチップであってもよい。以下で説明する各段階により、各マイクロLEDチップ30は、チップ維持フィルム20から分離され、PCBなどの基板40にボンディングされる。このとき、チップ維持フィルム20上の各マイクロLEDチップ30の間隔又は配列と、基板40上に実装されなければならない各マイクロLEDチップ30の間隔又は配列とは異なるが、本発明は、各マイクロLEDチップ30をチップ維持フィルム20からピックアップするとき、基板40上の目標とする一定の配列と一致する配列で各マイクロLEDチップ30の位置を調整する。

#### [0061]

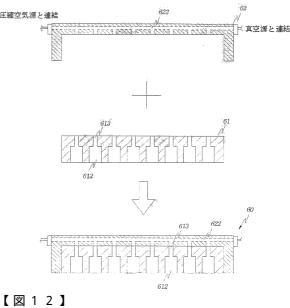

図11を参照すると、段階(s1)は、基板上に各マイクロLEDチップ30をアレイしようとする既に決定された配列と一致する配列の各チップポケット612が形成されたマルチチップキャリア60を準備する段階である。段階(s1)によって準備されたマルチチップキャリア60は、チップ維持フィルム20(図10参照)上の各マイクロLEDチップ30(図10参照)を前記既に決定された配列と一致するように調整した後、基板40(図10参照)上にプレーシングするのに用いられる。基板上への各マイクロLEDチップの既に決定された配列と各チップポケット612の配列とが同じであることは、隣り合う二つのマイクロLEDチップ間のピッチ(各中心間の間隔)と、隣り合う二つのチップポケット612、612間のピッチ(各中心間の間隔)とが一致することを意味する。

#### [0062]

マルチチップキャリア準備段階(s1)は、各チップポケット612が形成されたサク

20

30

40

50

ションプレート61と、真空及び空気加圧通路622が形成されたチャック62とを、真空及び空気加圧通路622が各チップポケット612と通じるように結合することを含む。真空及び空気加圧通路622は、チップポケット612内部の圧力を減圧し、マイクロLEDチップ30をチップポケット612内に吸入するために真空源と連結され、真空を発生できる通路である。

#### [0063]

チップポケット 6 1 2 内の圧力を増加させると、マイクロLEDチップ 3 0 (図 1 0 参照)を大きな圧力で押し出せるが、このために、真空及び空気加圧通路 6 2 2 は、チップポケット 6 1 2 内の圧力を増加させるのに利用可能である。

#### [0.064]

特許請求の範囲に記載の真空及び空気加圧通路は、空気加圧通路を兼ねる真空通路であってもよく、空気加圧通路と真空通路を全て含む通路であってもよい。

#### [0065]

サクションプレート61は、Si、GaAs、サファイア又はA1Nなどの材料からなるプレートに各チップポケット612が第1深さで形成され、各チップポケット612と連結される各連結ホール613が前記第1深さより小さい第2深さで形成されて製作される。チップポケット612の断面積は、マイクロLEDチップ30の断面積よりやや大きく形成されることが好ましい。連結ホール613は、チップポケット612の上端面にマイクロLEDチップ30の断面サイズより小さく形成され、チップポケット612の内部にサクションが発生するとき、チップポケット612の上端面は、マイクロLEDチップ30がこれ以上上昇しないように規制する。チップポケット612及び連結ホール613はエッチングによって形成される。前記第1深さは10μm乃至2000μmで、前記第2深さは1μm乃至100μmであることが好ましい。

#### [0066]

チャック62は、サクションプレート61の連結ホール613を介してサクションプレート61のチップポケット612と通じている真空及び空気加圧通路622を含むように製作される。より具体的に説明すると、真空及び空気加圧通路622を通じた真空の発生によってチップポケット612内の内部圧力が真空圧状態まで減圧され、マイクロLEDチップ30(図10参照)をチップポケット612にピックアップできる構造と、真空及び空気加圧通路を通じてチップポケット612内の内部圧力を高め、マイクロLEDチップ30を基板40(図10参照)にボンディングするときにマイクロLEDチップ30を気圧力で加圧できる構造とを含むようにチャック62が製作される。

#### [0067]

このとき、チャック 6 2 は、鉄及びセラミック種類或いはテフロン(登録商標)材質や プラスチック種類の材質を用いて加工してもよい。

#### [0068]

上述したように製作されたマルチチップキャリア 6 0 は、以下で説明する各後続段階に 用いられる。

#### [0069]

図 1 2 乃至図 1 4 を参照すると、各チップポケット 6 1 2 のそれぞれ、各マイクロ L E Dチップ 3 0 のそれぞれを一つずつキャプチャリングする段階 ( s 2 ) が行われる。

# [0070]

キャプチャリングする段階(s2)は、まず、図12及び図13に示したように、各チップポケット612のそれぞれが、それに対応するマイクロLEDチップ30と少なくとも部分的に面するようにマルチチップキャリア60をアラインした後で行われる。このとき、各チップポケット612とマイクロLEDチップ30の配列及びピッチは異なるが、各チップポケット612のそれぞれが該当のマイクロLEDチップ30と部分的に面すると、以下で説明するように、チップポケット612内の減圧が発生したとき、マイクロLEDチップ30がチップポケット612内に入り込みながら、各マイクロLEDチップ30の配列及びピッチが各チップポケット612の配列及びピッチと一致するようになる。

20

30

40

50

#### [0071]

次に、図13及び図14に示したように、キャプチャリングする段階(s2)では、真空源を駆動させ、各チップポケット612の内部を減圧し、各チップポケット612のそれぞれがマイクロLEDチップ30を吸入して収容できるようにする。チップポケット612内に吸入されたマイクロLEDチップ30は、連結ホール613が形成されているチップポケット612の上端面まで上昇し、そのチップポケット612の上端面によってこれ以上上昇できずに規制される。すなわち、連結ホール613がマイクロLEDチップ30によって塞がれ、真空によるサクションは継続して発生しているので、マイクロLEDチップ30は、チップポケット612内の上端面と接した状態で停止して固定される。このとき、チップポケット612の深さがマイクロLEDチップ30の厚さより大きいので、以後のマイクロLEDチップ30を基板上にプレーシングする段階では、マイクロLEDチップ30がチップポケット612に沿って十分な力を受けて下降できる十分な距離が確保される。

# [0072]

キャプチャリング段階(s2)では、チップポケット612内の真空発生を通じた吸入作用と共に、チップ維持フィルム20の底面で各マイクロLEDチップ30を各チップポケット612に対して押す作用が伴われる。チップ維持フィルム20の底面で各マイクロLEDチップ30を各チップポケット612に対して押すために、各チップポケット612に対応する各ヒレ71を含むマルチヒレ構造物70が用いられる。チップ維持フィルム20に維持されている各マイクロLEDチップ30の配列が均一でないとしても、各チップポケット612がサクション作用をすると共に、各ヒレ71が各マイクロLEDチップ30のそれぞれを各チップポケット612のそれぞれに押し入れる作用をするので、各マイクロLEDチップ30が各チップポケット612に容易に入り込んで収容される。チップ維持フィルム20の底面で各マイクロLEDチップ30を各チップポケット612に対して押す各ヒレ71を用いるにおいては、チップ維持フィルム20が柔軟性を有することが前提となる。

#### [0073]

次に、図15及び図16に示したように、各チップポケット612の配列通りに各LE Dチップ30を基板40上にプレーシングする段階(s3)が行われる。

### [0074]

プレーシングする段階(s3)は、基板40上の各ソルダー50と、チップポケット612にキャプチャリングされた各LEDチップ30とを対応させるように、基板40とマルチチップキャリア60をアラインした後で行われる。フリップチップ型LEDチップのように、下部に二つの極性を有する二つの電極を含むLEDチップの場合は、該当のLEDチップの二つの電極にボンディングされる二つのソルダー部分を一つのソルダーと見なす。よって、図15及び図16において、一つのマイクロLEDチップ30に対応する該当のソルダー50は、実際にLEDチップ30の底面に形成された二つの電極パッドにボンディングされる二つのソルダー部分を含む。

# [0075]

また、プレーシングする段階(s3)は、マルチチップキャリア60を基板40にアラインさせた状態で、各チップポケット612内部の減圧状態を解除し、マイクロLEDチップ30が基板40上に落下しながらプレーシングされるようにする。このとき、各チップポケット612の内部に加圧空気を供給すると、マイクロLEDチップ30が空気加圧力によって基板40上に強く加圧され、後続する段階でボンディング又は仮付着の接合力を増大させるのに寄与する。上述したように、各マイクロLEDチップ30は、図16に示した矢印方向に一定距離だけ下降しながら基板40上にプレーシングされる。このとき、各チップポケット612の内側面は、各マイクロLEDチップ30の下降をガイドする役割をし、その結果、より精密な各マイクロLEDチップのアレイを可能にする。

#### [0076]

図16及び図17に示したように、プレーシング段階( s 3 )に連続して、又はそれと

ほぼ同時に、基板 4 0 上の各ソルダー 5 0 を加熱し、各マイクロLEDチップ 3 0 を基板 4 0 上にボンディングする段階(s 4)が行われる。本実施例において、ボンディングする段階(s 4)は、基板 4 0 と接触する発熱ブロック 9 0 を用いて基板 4 0 上の各ソルダー 5 0 を加熱することによって行われる。このように発熱ブロック 9 0 を用いると、プレーシング段階(s 3)でマイクロLEDチップ 3 0 に加えられる下方加圧力を、マイクロLEDチップ 3 0 を実装するための加圧力として利用可能である。代案的に、ボンディングする段階(s 4)は、常温で各マイクロLEDチップ 3 0 を基板 4 0 に仮接させた後で行われるが、この場合、発熱ブロック 9 0 を用いることなくリフロー工程を通じて行われてもよい。

[0077]

図18は、基板40及びその基板40上にアレイされた各マイクロLEDチップ30が

図18は、基板40及びその基板40上にアレイされた合マイクロLEDチック30ヵ 発熱ブロック90(図17参照)から分離された状態を示す。

#### 【符号の説明】

[0078]

- 7 接着フィルム

- 8 トランスファーフィルム

- 9 加圧ローラー

- 20 チップ維持フィルム

- 30 マイクロLEDチップ

- 32 a、32 b 電極パッド

- 40 マウント基板

- 45a、45b 電極

- 50 ソルダー

- 60 マルチチップキャリア

- 61 サクションプレート

- 62 チャック

- 70 マルチヒレ構造物

- 71 ヒレ

- 90 発熱ブロック

- 612 チップポケット

- 6 1 3 連結ホール

- 614 サクションホール

- 622 真空及び空気加圧通路

- 6 1 2 1 スロープ

#### 【要約】

【課題】マイクロLEDチップアレイ方法を開示する。

【解決手段】サクションホールを通じて減圧される複数のチップポケットが形成されたマルチチップキャリアを準備する段階と、各マイクロLEDチップが各チップポケットの底に密着し、各マイクロLEDチップを各チップポケットにキャプチャリングする段階と、各チップポケットにキャプチャリングされた各マイクロLEDチップを基材上にプレーシングする段階とを含み、各チップポケットのそれぞれは、底より大きい幅を有する入口から底までつながったスロープを含み、スロープにより、基材上にプレーシングされた各マイクロLEDチップの中心間の間隔と各チップポケットの中心間の間隔とが同一であることを特徴とするマイクロLEDチップアレイ方法を提示する。

# 【選択図】図2

20

10

30

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

# 【図13】

# 【図14】

# 【図15】

# 【図16】

【図17】

【図18】

#### フロントページの続き

(51) Int.CI. F I

H 0 5 K

13/02

(2006.01)

H 0 5 K

13/02

E

G 0 9 F

9/33

(2006.01)

G 0 9 F

9/33

G 0 9 F

9/00

(2006.01)

G 0 9 F

9/00

3 3 8

(72)発明者 キム,ボギュン

大韓民国 17086 京畿道 龍仁市 器興区 ウォンゴメ路 12

(72)発明者 キム,グンハ

大韓民国 17086 京畿道 龍仁市 器興区 ウォンゴメ路 12

(72)発明者 ムン,ジュギョン

大韓民国 17086 京畿道 龍仁市 器興区 ウォンゴメ路 12

# 審査官 皆藤 彰吾

(56)参考文献 特開2016-066765(JP,A)

特開2003-031847(JP,A)

特開2002-267893(JP,A)

国際公開第2017/075776(WO,A1)

特許第6170232(JP,B1)

特開昭58-50578(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 33/00-33/64

G09F 9/00

G09F 9/33

H01L 21/60

H01L 21/673

H01L 21/677

H 0 5 K 1 3 / 0 2

H 0 5 K 1 3 / 0 4

| 专利名称(译)       | 用于制造LED显示面板的微LED芯片阵列方法和用于其的多芯片载体                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|

| 公开(公告)号       | JP6545889B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2019-07-17 |  |  |

| 申请号           | JP2018230832                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2018-12-10 |  |  |

| 申请(专利权)人(译)   | 流明有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |

| 当前申请(专利权)人(译) | 流明有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |

| 发明人           | ユ,テキョン<br>ソ,ジュオック<br>キム,ボギュン<br>キム,グンハ<br>ムン,ジュギョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |

| IPC分类号        | H01L33/48 H01L21/673 H01L21/677 H01L21/60 H05K13/04 H05K13/02 G09F9/33 G09F9/00                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |

| CPC分类号        | H01L21/67132 H01L21/67144 H01L24/13 H01L24/16 H01L24/29 H01L24/32 H01L24/75 H01L24/81 H01L24/83 H01L24/97 H01L25/0753 H01L2224/131 H01L2224/16227 H01L2224/291 H01L2224/32227 H01L2224/75745 H01L2224/7598 H01L2224/81005 H01L2224/81143 H01L2224/81192 H01L2224 /81201 H01L2224/81203 H01L2224/81815 H01L2224/81986 H01L2224/83005 H01L2224/83201 H01L2224/83203 H01L2224/83815 H01L2224/83986 H01L2224/97 H01L2924/12041 H01L2224/81 H01L2924/014 H01L2924/00012 H01L2924/00014 H01L2224/83 H01L24/95 H01L27/156 H01L33/005 H01L33/48 |         |            |  |  |

| FI分类号         | H01L33/48 H01L21/68.U H01L21/68.B H01L21/60.311.T H05K13/04.B H05K13/02.E G09F9/33 G09F9 /00.338                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |  |  |

| F-TERM分类号     | 5C094/AA43 5C094/BA25 5C094/CA19 5C094/DB01 5C094/EB10 5C094/FA02 5C094/FB02 5C094 /FB14 5C094/GB01 5C094/JA09 5E353/BB08 5E353/HH08 5E353/HH51 5E353/JJ19 5E353/MM03 5E353/MM08 5E353/QQ01 5E353/QQ11 5E353/QQ15 5F044/PP17 5F131/AA04 5F131/BA54 5F131 /CA18 5F131/DA03 5F131/DA43 5F131/DA54 5F131/DB22 5F131/GA05 5F131/GA23 5F131/GA66 5F131/GA68 5F142/AA54 5F142/FA32 5F142/FA34 5F142/FA38 5F142/GA02 5G435/AA17 5G435 /BB04 5G435/CC09 5G435/KK05                                                                              |         |            |  |  |

| 优先权           | 1020180018125 2018-02-14 KR<br>1020180123402 2018-10-16 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |

| 其他公开文献        | JP2019140380A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |  |  |

| 外部链接          | Espacenet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |

# 摘要(译)

公开了一种微型LED芯片阵列方法。 解 将捕获在每个芯片口袋中的每个微型LED芯片捕获并放置在基板上,每个芯片口袋从宽度大于底部的入口到底部连接。 一种具有斜率的微型LED芯片阵列方法,其中,每个微型LED芯片的中心距与放置在基板上的每个芯片袋的中心距相同。 要做。 [选择图]图2

(19) **日本国特許庁 (JP)**

(12)特許公報(B1)

(11)特許番号 特許第6545889号

(54) [発明の名称] LEDディスプレイパネル製造のためのマイクロLEDチップアレイ方法及びこれに用いられる マルチチップキャリア